# United States Patent [19]

## Oguchi

[56]

[11] Patent Number:

4,545,014

[45] Date of Patent:

Oct. 1, 1985

| F 3                                |            |                                            |  |  |

|------------------------------------|------------|--------------------------------------------|--|--|

| [75]                               | Inventor:  | Tetsuji Oguchi, Tokyo, Japan               |  |  |

| [73]                               | Assignee:  | Nippon Electric Co., Inc., Tokyo,<br>Japan |  |  |

| [21]                               | Appl. No.: | 325,086                                    |  |  |

| [22]                               | Filed:     | Nov. 25, 1981                              |  |  |

| [30]                               | Foreign    | n Application Priority Data                |  |  |

| Nov. 26, 1980 [JP] Japan 55-166297 |            |                                            |  |  |

| [51]                               | Int. Cl.4  | G06F 9/00                                  |  |  |

| Ī52Ī                               | U.S. Cl    |                                            |  |  |

|                                    |            | arch 364/200, 900                          |  |  |

[54] INFORMATION PROCESSING APPARATUS

#### **References Cited**

### U.S. PATENT DOCUMENTS

| 4,044,240 | 8/1977 | Cox, Jr. et al  | 364/300 |

|-----------|--------|-----------------|---------|

| 4,166,945 | 9/1979 | Inoyama et al   | 364/900 |

|           |        | Brickoian et al |         |

Primary Examiner—Gareth D. Shaw Assistant Examiner—John G. Mills Attorney, Agent, or Firm—Sughrue, Mion, Zinn, Macpeak, and Seas

### [57] ABSTRACT

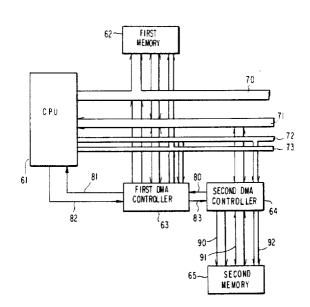

An information processing apparatus employs first and second direct memory access controllers which cooperate during transfer of information between first and second devices, e.g. memories. The first controller controls information transfer from the first memory to the second controller and the second controller transfers the information from its own internal storage to the second memory while simultaneously receiving further information under the control of the first controller. The second controller includes address control circuitry for high speed generation of non-sequential addresses for writing into the second memory.

### 1 Claim, 8 Drawing Figures