### NEC µPD7220/72120 Related Public Documents

- <u>ISSCC</u> (International Solid-State Circuit Conference)

- μPD7220A User's Manual

- Nikkei Electronics Magazine (µPD7220)

- Transistor Gijutsu (Technology) Magazine (<u>µPD7220</u>)

- Transistor Gijutsu (Technology) Magazine (µPD7220A)

- Nikkei Electronics Magazine (µPD72120)

- µPD72120 User's Manual

Go to <a href="https://www.oguchi-rd.com/LSI%20products.php">https://www.oguchi-rd.com/LSI%20products.php</a> to get more detailed NEC  $\mu$ PD7220/72120 related information such as;

"Logic Schematics", "Design Notes", "Evaluation Board Schematics", "Evaluation Software", "Silicon Die Photos", "Newspaper", "Magazine", and so forth.

Go to <a href="https://www.oguchi-rd.com/patents.php">https://www.oguchi-rd.com/patents.php</a> to get patent information including NEC μPD7220/72120 related patents.

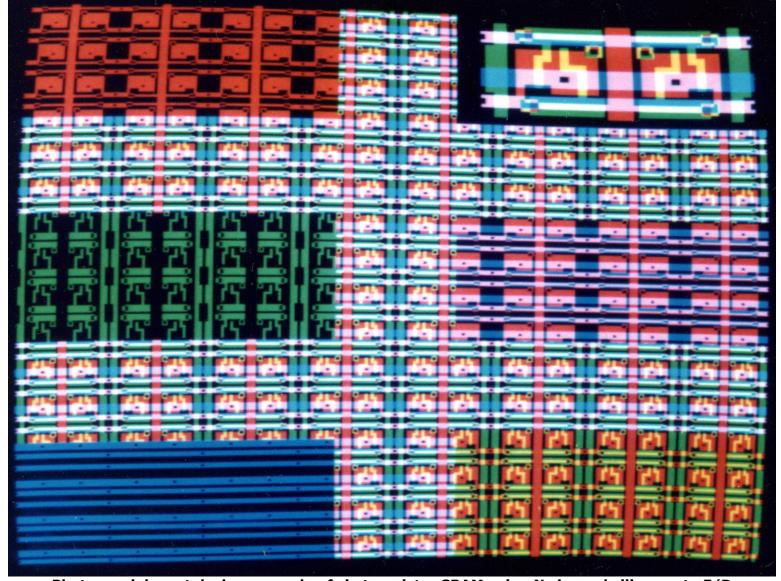

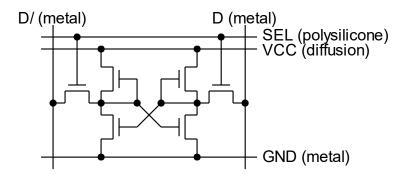

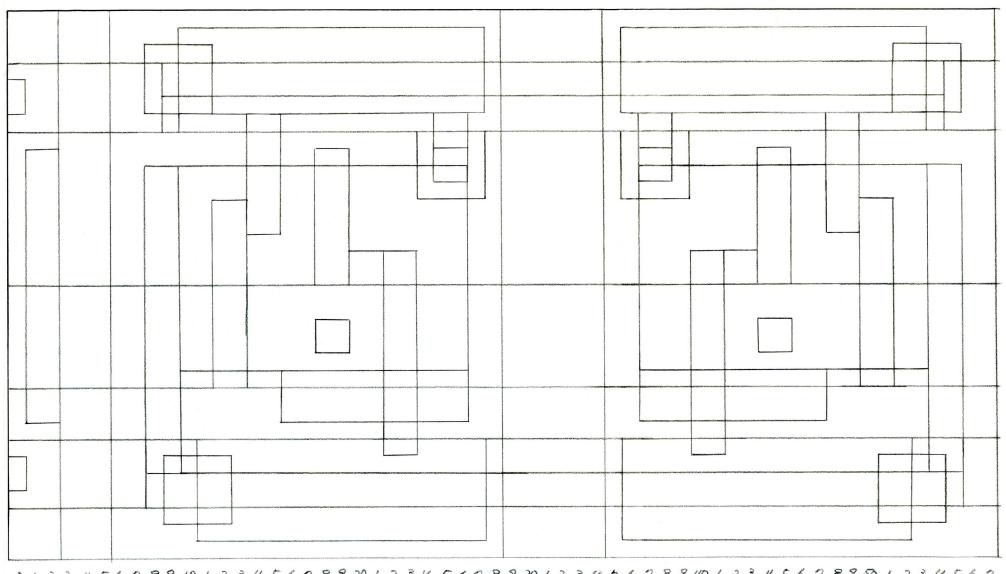

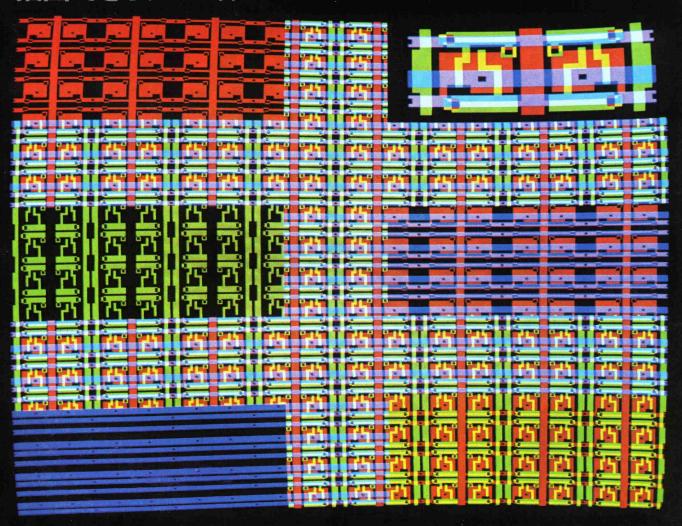

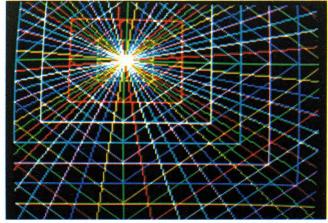

Photo mask layout design example of six transistor SRAM using N channel silicon gate E/D (Enhancement-mode for gate, Depletion-mode for load) MOS transistors for front cover of this issue

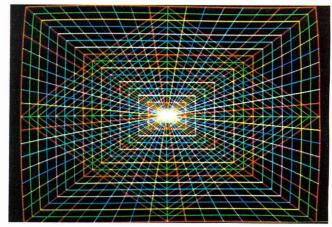

I created this graphics image in one day using  $\mu PD7220$  demo system controlled by Tandy TRS-80 personal computer I privately purchased in May, 1978, brought into laboratory in NEC for decorating front cover sheet of this issue of Nikkei Electronics magazine.

Red (赤): diffusion layer (拡散層), Green (緑): poly-silicon layer (ポリシリ層), Blue (青): Metal (aluminum) layer (アルミ層), Contacts between metal and diffusion layer, Contacts between poly-silicon and diffusion layer

The thesis was related to computer color graphics. Therefore, it achieved distinction of printing by colors for the first time. I specified the colors and created front page image based upon the deputy editor-in-chief Syozo Watanabe's (Nabe-cho) request. Photographer Gengo Aida from Nippon Keizai Shinbun newspaper, came in twice to take a photo of the front cover using 35mm camera once and using 6x9 cm Brownie large camera next day.

012345678910123456789201234567893012345678940123456789501234567

NIKKEI RAM CELL ( CELL, MAGCELL , [ ELEASM/CIM]

1981 10-12

16 ビット・マイクロコンピュータ用 OS 小型で簡便な各種センサの開発 電圧共振型 DC-DC コンバータ

5

7

8

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

1ドットを 800 ns で 最初は記憶を記し 描画できるグラフィック・コントローラ LSI

# 1ドットを 800 ns で描画できる ラスタ走査 CRT 用 グラフィック・コントローラ LSI

要点 文字表示制御機能と、ドット単位のグラフィック描画機能とを1チップ上に集積した、ラスタ走査 CRT 用のグラフィック・ディスプレイ・コントローラ (GDC)の概要を紹介している。GDC は1万3000素子を集積した MOS LSI だが、新開発した描画アルゴリズムにより、加減算だけで描画アドレスを算出できる。このため、クロック周波数5 MHz の時、1 ドットを800 ns で描画できる。GDC が制御する最大容量256 K 語×16 ビットの映像メモリーは、システム・バスから分離されているため、装置のCPU がコマンド/パラメータ作成中でも、GDC は並列に描画を実行できる。 (本誌)

小口 哲司 日本電気 集積回路事業部 マイクロコンピュータ・システム部

文字や図形を表示するグラフィック装置には、電子線走査方式と表示管面構造との組み合わせによって、次の3種類のCRTが使用されている。

- (1) ランダム走査リフレッシュ型

- (2) ランダム走査蓄積管型

- (3) ラスタ走査リフレッシュ型

ランダム走査型 CRT は、任意の点から任意の方向に任意の点まで走査できるので、開始点、終了点などのベクタ情報を記憶するメモリーのみを持てばよい。一方、ラスタ走査型 CRT は、一定の周期と間隔で CRT 上を電子線が移動する方式で、テレビジョン放送受信用として一般家庭に普及している。後者は、前者に比べて多色化、多階調化などが容易にできる。反面、1 画面分以上の画素を記憶する大容量メモリーが要るため、コスト高になるのが難点だった。しかし、記憶素子の価格が集積度の向上によって大幅に低下してきたため、ラスタ走査型 CRT を用いたグラフィック装置は急速に普及しつつある。

ラスタ走査型 CRT 用の、文字表示制御だけを行う CRT コントローラ(CRTC)は、既に多数発表されている。しかし、最近では、文字単位の表示制御だけではなく、1ドット単位で、細かく表示/描画するような制御機能が、オフィス・コンピュータ用の CRT 端末や通信端末装置にも求められつつある。更に、文字

表示についても、漢字表示やワード・プロセサ端末装置として、 従来型 CRTC にはない、より高度な機能、設計自由度の高さが 求められている。

これらの要求に応えるため、高度な文字表示制御機能、およ び1ドット単位で高速にグラフィック描画する機能を、1チッ プに集積したグラフィック・ディスプレイ・コントローラ LSI (GDC: graphic display controller。以下, この LSI を単に GDC と呼ぶ)を開発した。この GDC は、従来の高度なグラフ ィック装置に採用されているような、ビット・スライス CPU や TTL(transistor transistor logic), PLA(programmable logic array) などで構成されるグラフィック表示/描画回路を、その まま集積回路化したのではない。バイポーラの乗算器などを使 わなくても高速動作できるような描画アルゴリズムを新たに開 発し、MOS LSI 化したものである。LSI 上には、グラフィック 機能のほか, 文字表示制御機能も集積してある。このため, 簡 単な文字表示制御から高級なカラー・グラフィック表示/描画制 御まで、広範囲に使える。更に、表示機能を使用せずに表示と は無関係な大容量メモリーの制御用としても利用できる(ここ で、「表示」とは GDC が映像メモリーの内容を読み出す操作、 「描画」とは映像メモリーに書き込む(書き換える)操作を言う。 以下も同じ)。

NIKKEI ELECTRONICS 1981. 10. 12

どのような描画方向に対する直線描画であろうと、円弧描画であろうと、GDC の描画速度はドットの修正時間を含み、一律に 800 ns/ドット(クロック周波数 5 MHz 時)である。これは、既存のグラフィック装置の描画速度よりもかなり速い。例えば、描画用プロセサとしてバイポーラ・ビット・スライス CPU 4 個構成の 16 ビット CPU とワード長 56 ビットの ROM(read only memory)、RAM(random access memory)とで構成される高級なグラフィック装置が発表されている。りその装置の描画速度は  $1.12 \, \mu \text{s}/ドットであり$ 、GDC が達成した描画速度には及ばない。更に、従来装置はソフトウェアで描画処理を行うので、描画種類(円、直線など)や描画方向が異なると、描画速度が大きく変動してしまう。

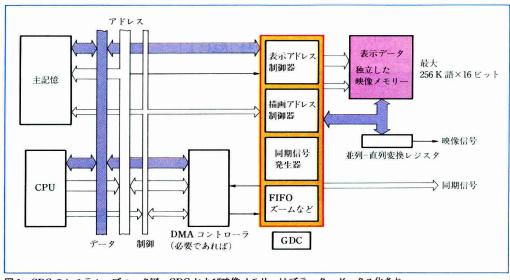

#### 映像メモリーをシステム・バスから切り離す

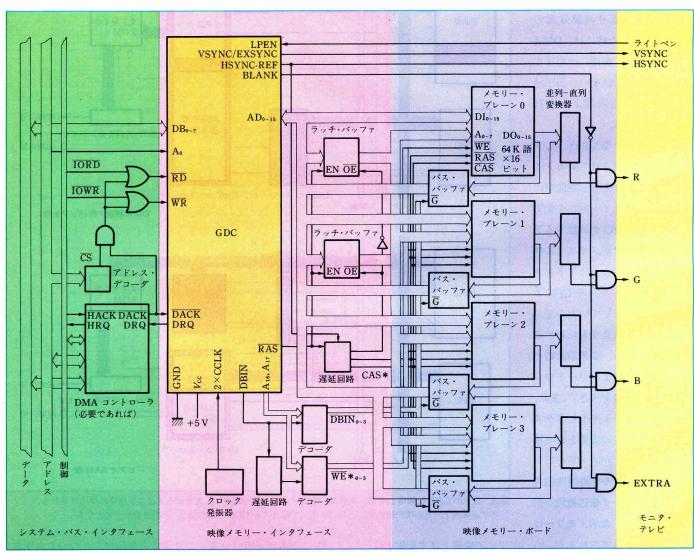

GDCは、最大 256 K 語×16 ビット(1024×1024 ドットのメモリー・プレーンであれば 4 枚分)の大容量映像メモリーを自分自身で直接制御する。この映像メモリーは、装置の CPU が制御するシステム・バスから分離されている(図 1)。つまり、映像メモリーに対して読み出し/修正変更/書き込みを行うのは、CPU ではなく、GDC 自身である。このように、映像メモリーをシステムの主記憶から分離した構造にできるため、従来型CRTC(別掲「従来の CRT 制御用 LSI」、pp. 190-191 参照)のように、システム・バスの衝突に対して注意を払う必要はない。

GDC がシステム・バスの使用権を要求するのは、DMA (direct memory access) 転送要求時だけである。そのため、映像メモリーに対して GDC が描画処理を実行中であっても、CPU は別の処理、例えば次の描画のためのコマンド作成に専念できる。

一般に、座標入力から表示ま でのグラフィック装置の動作 は、次のように区分できる。

① ディジタイザやあらかじ め作成されているリストなどか ら座標データを取り出す (座標 入力)。この時 CPU 自身が座標 を発生することもある。

②座標データを基にして変換処理などを行い,よりマイクロ なコマンド/パラメータを作成する(描画前処理)。

③ コマンド/パラメータを基にして描画アドレス計算を行う (描画処理)。

④ 映像メモリーにアドレスを供給し、データの修正・変更動作を行う (描画実行)。

⑤ 常時,表示アドレス演算をし,映像メモリーへアドレスを 供給し表示データを読み出す (表示)。

⑥ 常時, 同期信号を発生しモニタ・テレビに供給すると共に表示/描画のタイミング制御をする(同期信号発生)。

今回製品化した GDC は, このうち, ③, ④, ⑤, ⑥ の処理, 制御を CPU の関与なしに行う。従来の装置では, ③, ④を CPU が処理しているため、描画速度が遅い。

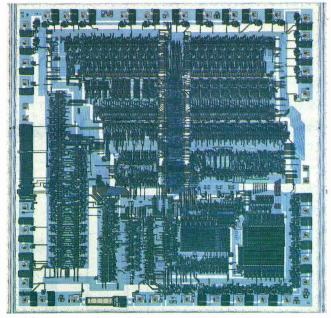

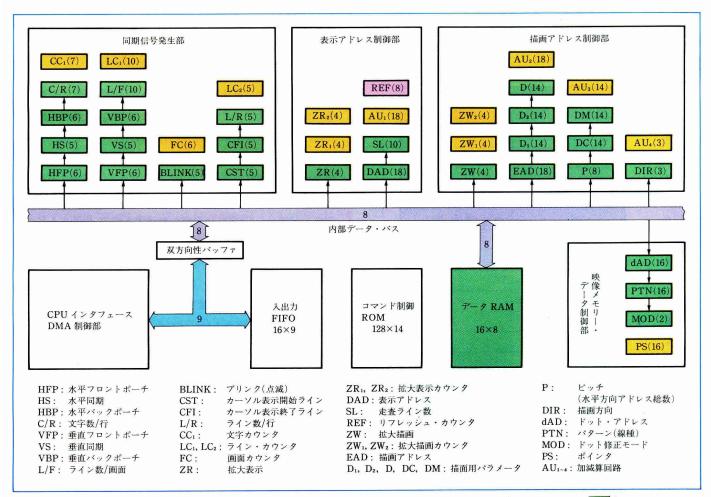

#### LSI の内部構成

図 2(a)は、GDC のチップ写真、(b)はそのブロック図である。図 2(b)に示すように、GDC は入出力 FIFO(first in first out)、コマンド制御 ROM、データ RAM、同期信号発生部、表示アドレス制御部、描画アドレス制御部、映像メモリー・データ制御部、それに CPU インタフェース/DMA 制御部で構成される。各部は、同図のように 9 ビットと 8 ビット幅の 2 種類の内部データ・バスで結ばれている。表示アドレス制御部や描画アドレ

図1 GDC のシステム・ブロック図。GDC および映像メモリーはブラック・ボックス化され、 独立して動作する I/O 機器としてとらえることができ、拡張性に富む

ス制御部などは、互いに関連を保ちながらも独立に並行動作する必要があるため、それぞれ固有のカウンタ、演算器、シフタを持たせている。以下、各部の構成と機能の概略を紹介しておく。

▶入出力 FIFO: 16 語×9 ビットの容量を持ち、CPU から送られてくるコマンド/パラメータを一時記憶する。逆に CPU が映像メモリーや GDC の内部レジスタの内容を読み出す場合も、それらのデータはこの FIFO を経由して読み出される。つまり、DMA 転送時を除けば、CPU と GDC (および映像メモリー) 間のデータ転送は、すべてこの双方向 FIFO を介して行われる。GDC が描画を実行中でも、この FIFO がいっぱいでなければ、CPU は GDC にコマンド/パラメータを送れる。なお、FIFO の9 ビット目には、データ・バス上の8 ビット・コードがコマンドかパラメータかを示すビットが記憶される。

▶コマンド制御 ROM: 128 語×14 ビット構成で、コマンドの解釈や、表示領域切り替え時に表示アドレス制御部から発生される内部割り込みの処理、データ RAM の制御などを行う。

▶描画アドレス制御部: 18 ビットの描画アドレス・レジスタ EAD や, グラフィック文字描画時に 1~16 倍の係数を設定する

図2(a) GDC チップ。ゲート長 3 μm の n チャネル・シリコン・ゲート E/D MOS トランジスタ 1 万 3000 個を搭載する。チップ・サイズは 5.29×5.39 mm。高速並列演算を実行するためハード・ワイアド論理を用いる。規則性のある繰り返し回路にまとめ、マスク・レイアウトを容易にしている

ための拡大描画用レジスタ ZW, 更に描画パラメータを記憶す る5本の14ビット・レジスタDC, D, D<sub>1</sub>, D<sub>2</sub>, DM を持つ。 別掲記事「描画アルゴリズムの改善」, pp. 202-205 で述べるよう な描画アルゴリズムに従って、所定の演算を行い、描画(ワー ド) アドレス EAD およびドット・アドレス dAD を生成する。 整数加減算回路を3組(AU2~AU4)持ち,前記の描画アルゴリ ズムに基づく演算と EAD, dAD の生成を 4 クロックで並行に 行う。

▶表示アドレス制御部:18ビットの表示アドレス・レジスタ DAD. 8ビットのリフレッシュ・アドレス・レジスタ REF を持 ち、表示アドレス、リフレッシュ・アドレスを生成する。また、1~ 16 倍の拡大表示係数を設定するためのレジスタ ZR を持つ。

- ▶同期信号発生部:各種のパラメータ・レジスタ (図 2(b)の同 ブロックに示す)の設定値に基づいて、水平・垂直同期信号や 表示消去信号などを発生する。

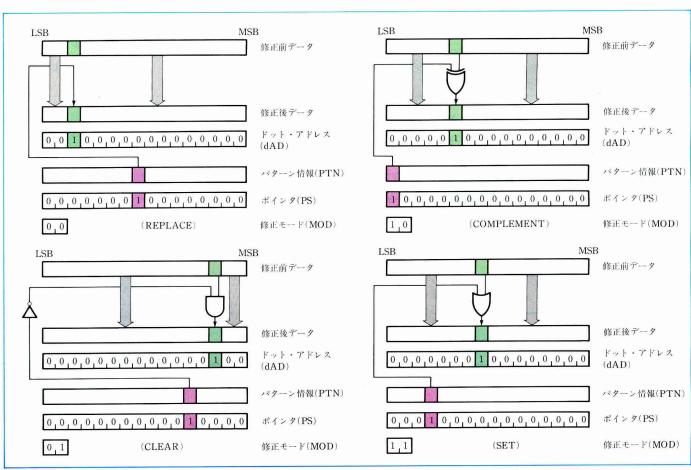

- ▶映像メモリー・データ制御部:グラフィック描画に必要なド ット単位の修正を行う。つまり、映像メモリーから読み出した データと、直線、破線などの線種を記憶する16ビットのレジス タ PTN、および dAD の内容を比較し、後述するような方法で 映像メモリーの内容をビット単位で修正する。

- ▶データRAM: 16語×8ビット構成で、表示開始アドレス SAD や表示領域設定ライン数 SL, 描画時に使用される 16 ビッ トの線種データ、8バイト構成のグラフィックス文字描画用ド ット情報を一時的に記憶する(図3)。これらの値の設定は, CPU

図 2(b) GDC のレジスタ・レベル・ブロック図。従来型 CRTC は同期信号発生部と表示アドレス制御部の一部しか集積していない。 タはプログラムで任意値に設定できる。各レジスタ群は 🧰 で示す専用のカウンタや演算器を持ち、内部データ・バスとは別経路で並列動作する

が SCROLL コマンドによって行う。実際の表示/描画処理時には、表示アドレス制御部などの独立した閉ループ回路内で処理するため、これらのデータは前もって図 2(b)中の DAD、SL、PTN などのレジスタへ転送される。

▶ CPU インタフェース・DMA 制御部: 一般の 8 ビットまたは 16 ビット・プロセサと接続するためのインタフェース部。 8 ビットの双方向性データ・バス (DB<sub>0~7</sub>), アドレス・ライン (A<sub>0</sub>), 書き込み信号 (WR), 読み出し信号 (RD) などがシステム・バスから供給される (図 4)。また、DMA 制御部は、映像メモリーと主記憶間の DMA 転送を制御する。映像メモリーのアドレス不連続部を含む矩形領域データについて、主記憶との間で双方向のメモリー-メモリー間 DMA 転送を可能にする。

#### 映像メモリーに対する描画を4クロックで行う

GDC の内部回路は、外付け回路から供給する単相クロックと

図3 内蔵データ RAM マップ。コマンドによって任意なアドレス からデータを設定できる。下位 8 バイトは表示用, 上位 8 バイトは描 画時,線種情報記憶用または文字ドット情報記憶用として使用する

同一周波数の2相クロックを内部で発生し、そのクロックに同期して動作する。クロック周波数は、ラスタの1水平走査内表示区間の表示時間と、その時の映像メモリーへのアクセス数(表示ドット数に依存する)によって決定される。図4に示したように、GDCは映像メモリーに対して1回のアクセス(2クロック)で16ビット並列に読み出す。したがって、例えば、水平走

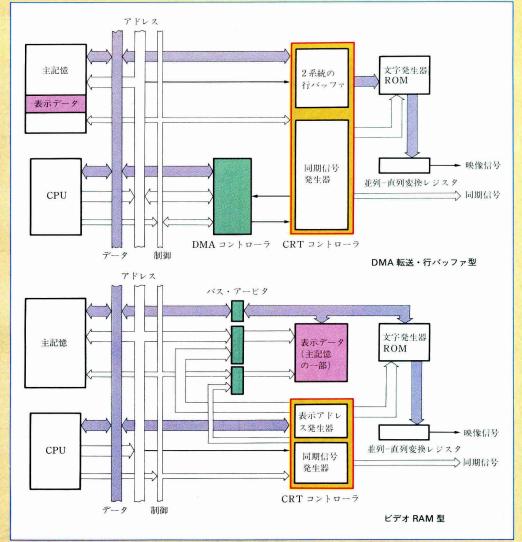

## 従来のCRT制御用LSI

従来から使用されている CRT 制御用 LSI (CRTC) は、文字表示制御を主目的として設計されている。これらは、大別して、① DMA 転送・行バッファ型と、② ビデオ RAM 型とに分類できる。両型式共に、表示データを格納するメモリーは CPU が直接制御する主記憶の一部にマッピングされる(図 A)。

DMA 転送・行バッファ型 CRTC は、最大 80 バイト程度の文 字コードと最大20バイト程度の文字属性制御コードを蓄積す る行バッファを2系統持つ。各々、現在行表示用と DMA 転送 される次行表示データ格納用として使用され、行表示の終了ご とに、その用途が反転する。短所は、行バッファ容量の上限が CRTCによって決まってしまい、拡張できないことである。こ のため、文字属性制御や1行中に表示できる文字数などが制限 されてしまい、装置設計上の自由度に欠ける。しかし、表示内 容を主記憶から CRTCに DMA 転送するので, 後述するビデオ RAM型 CRTC の場合とは異なり、バスの衝突や表示中のフラ ッシュの発生は起こらない。ただし、表示内容に変化がなくて も1行の表示終了ごとに、必ず DMA 転送を行う必要がある。 1行分のバッファしか内蔵していないからである。DMA 転送 のたびに CPU を停止させねばならず、キーボード制御や通信 制御などの CPU 本来の処理能力が低下する。1 行に 80 文字を 表示し、文字属性を付加した場合、DMA 転送によって CPU が 停止する比率は30~40%にも達する。グラフィック表示制御用 として、この DMA 転送方式は適さない。文字表示制御時には、 1行(例えば16ライン)走査期間内に最大100バイト程度の DMA 転送を行えばよいが、グラフィック表示制御時には、1ラ イン走査期間内に1ライン分の表示データをすべて転送せねば ならない。例えば、1水平走査時間が 64 μs の CRT を使用し、 1ラインに512ドット(64バイト)を表示する場合,1Mバイ

査周波数が 31.5 kHz の CRT に 1024×1024 ドットのインタレース表示を行う時、クロック周波数は約 5 MHz になる。

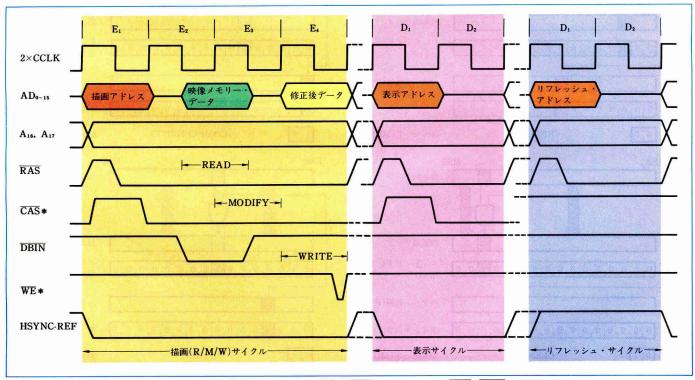

映像メモリーのアドレス・サイクルは、表示時およびリフレッシュ時には2クロック、描画時にはリード/モディファイ/ライト(R/M/W)動作を行うために4クロックに固定されている(図5)。映像メモリーの内容をGDCを経由してCPU側へ読み

出す場合も、GDC は描画時と同様、映像メモリーに対して R/M/W 動作を行うため、4 クロックかかる。

描画時の R/M/W 動作は次のような段階を踏む。まず、描画アドレス (EAD=18 ビット) が 16 ビットのアドレス/データ多重化出力端子  $AD_{0\sim15}$  およびアドレス出力専用端子  $A_{16}$ ,  $A_{17}$  から出力される。サイクルの最初の 1 クロック( $E_1$ )で出力され

ト/秒の高速で連続した DMA 転送を行う必要がある。この時, 表示期間中, CPU は完全に停止 してしまう。より高解像度の CRT を使用した時には, DMA 転送速度を更に高速にせねばな らず,実際的ではない。表示速 度は DMA 転送速度よりも高 速だからである。

ビデオ RAM 型 CRTC は,表 示データが格納されているメモ リーのアドレスを表示期間中に 供給する。メモリー内容を変更 する時には、CPUが供給するア ドレスとデータがメモリーに接 続される。このようにアドレス およびデータ・バスを CPU と 表示系とで共有しているので, バスの衝突を防止するための処 置が必要となる。装置設計時の ソフトウェアおよびハードウェ ア設計上の負担が大きい。また, 表示にフラッシュを生じさせず にメモリー内容の変更を行う場 合には、特に、バス・アービト レーションに費やす時間的損失 が大きく, データ転送機能が低 下してしまう。表示メモリーは

図 A 従来の CRT 制御用 LSI のシステム・ブロック図。両方式共に、表示データは主記憶中にマップされる。システム構成上の自由度や拡張性に乏しい。本文で紹介する GDC の場合は 部回路が不要となる

主記憶上にマップされるが、ハードウェア構成上は主記憶とは 独立した小規模なメモリー構成としなければならない (図 A 参 照)ことも、メモリー素子が安価で高集積化されつつある現在、 装置設計者を悩ませる一因ともなっている。 たアドレスはトライステート出力状態を持つオクタル・ラッチ回路に RAS(row address strobe)出力が高レベルの時にラッチされる(図 4 参照)。この RAS 信号は、一般的な 16 ピン・ダイナミック RAM に対する行・列アドレス切り替え信号の基準タイミング信号としても用いられ、外付け遅延回路によって発生タイミングがダイナミック RAM にとって最適となるように調整した後、ダイナミック RAMの RAS、CAS(column address strobe)端子に接続する。更に、アドレス・ラッチの出力を切り替え、GDC が供給する 16 ビットのアドレス信号を 8 ビ

ットに時分割された行・列アドレスとしてダイナミック RAM に接続する。 $E_2$  から  $E_3$  にかける 1 クロック間に, $\overline{DBIN}$  ( $\underline{d}$  at a  $\underline{b}$  us  $\underline{in}$ ) 信号を出力し,映像メモリーから読み出された 16 ビット・データをバス・バッファを介して映像メモリー・バスに載せ,一括して GDC 内に読み込む(read)。 $E_3$  の 1 クロックで,ドット修正モード定義情報(図 2 中の MOD)に従って,読み込まれたデータに修正を加える(modify)。 $E_4$  において GDC から修正後データを出力し, $\overline{DBIN}$  信号を外付け回路によって遅延させて生成するダイナミック RAM 書き込み信号 ( $\overline{WE}$ ) の立ち

図4 インタフェース・ブロック図。1024×1024 ドット 16 色グラフィック表示を簡単なインタフェースで実現できる。64 K ダイナミック RAM 64 個で構成する映像メモリー部を含め 1 枚のプリント基板上に実装できる

下がり時に映像メモリーに書き込む (write)。アドレスは、 $\overline{RAS}$  および  $\overline{CAS}$  の立ち下がり時にダイナミック RAM に取り込まれる。

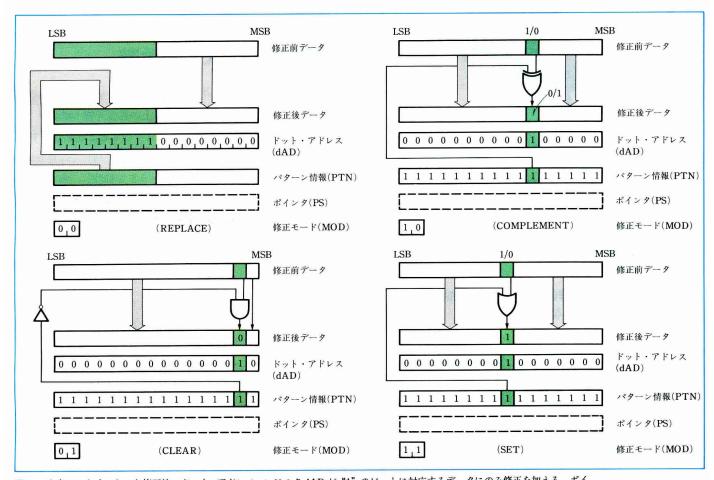

#### 1ドット単位の描画/修正が可能

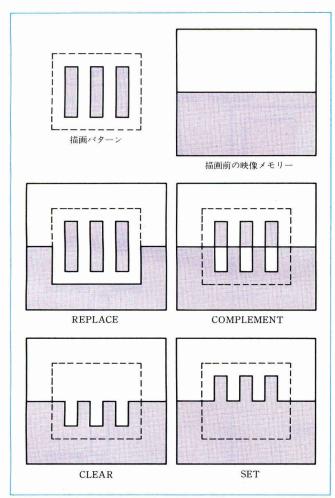

映像メモリー・データの修正は、映像メモリー・データ制御部において図6のようにして行っている。16 ビットのポインタ (PS) は16 ビットのパターン情報 (PTN) のうち1 ビットのみを指し示し、初期化動作時や直線、円弧などの描画終了時には最下位ビットのみが"1"となる。1 ドットの描画後、上位方向に1 ビットだけシフトし、PTN に対する指示位置を更新する。PS によって指示された PTN の1 ビットのみを EXOR (exclusive OR)、AND、OR などのドット修正ゲートの一方の入力として使用する。一方、16 ビットのドット・アドレス(dAD)は16 ビットの修正前データから修正を加えるべきビットを抽出し、修正ゲートに接続する。dAD が"0"であるビットに対応する修正前データはドット修正の対象とはならず、単に、GDC内を循環する。ドット修正モードは REPLACE、COMPLE-

MENT, CLEAR, SET の4種あり, 2ビットの MOD レジス 夕に修正の種別を格納しておく。図6に示すように REPLACE 時には修正前データは無視される。

REPLACE 以外の修正モードでは、パターン参照内容 (PTN レジスタ中の PS で指される内容) が "1" であるドットについてのみ修正を加え、"0" の場合には、単にメモリー内容を循環して再書き込みをする (図 7 参照)。この修正をドット単位の論理演算としてとらえるならば、パターンが"1"であるドットについて、各々、排他的論理和 (EXOR)、否定論理積 (NAND)、論理和 (OR) として動作する。異なる修正モードを組み合わせて使用したり、パターン内容を反転して設定すると、多彩な修正結果を得ることができる。

描画サイクル中であっても、表示アドレス制御部において表示およびリフレッシュのアドレス計算を行っている。表示サイクルには、表示アドレスのみが映像メモリーに供給される。図4の例では、1枚当たり16個の64Kビット・ダイナミックRAMで構成されるメモリー・プレーン4枚に搭載されるすべてのダ

図5 映像メモリー制御タイミング。3種のアドレス・サイクルを持つ。 $\overline{CAS}*$ , $\overline{RAS}*$ は各々基準信号 $\overline{RAS}$ , $\overline{DBIN}$ を外付け回路によって遅延し、最適なタイミングに発生させる。リフレッシュは HSYNC 時に行う

イナミック RAM に対して同一の RAS、CAS 信号が接続される。したがって、各メモリー・プレーンのダイナミック RAM 出力 DO から同時に 16 ビットずつの表示データが並列-直列変換レジスタに送られ、映像直列信号を得る。描画サイクル時には  $\overline{DBIN}$  と  $\overline{WE}$  信号を、この例ではメモリー・バンク切り替え用信号として使用されるアドレス信号  $A_{16}$ ,  $A_{17}$  によってデコードし、メモリー・プレーン選択を行うが、表示時には各メモリー・プレーンから同時に表示データを取り出す構成とする。1個のGDC で、 $1024 \times 1024$  ドットであれば、メモリー・プレーン 4枚、16 階調(色)を、 $512 \times 512$  ドットならば、メモリー・プレーン 16 枚、64 K 階調を取ることができる。後述する GDC の並列動作機能を用いれば、メモリー・プレーンの増設は制限なく行える。映像メモリーとしてダイナミック RAM を用いる設定を後

述する SYNC コマンドによって行うと、HSYNC 時にリフレッシュ・アドレスを AD<sub>0~15</sub> の下位 8 ビットから出力する。この時、アドレス・ラッチの下位 8 ビットの出力のみを有効とし、CAS 信号に立ち下がり状態が生じないように外付け回路で制御する(図 4)。RAS オンリー・リフレッシュが可能となる。表示期間中には連続したアドレスが映像メモリーに与えられるので、リフレッシュは特に行う必要はないと考えがちだが、拡大表示時やインタレース走査時、映像メモリーの一部のみを表示する時などに、ダイナミック RAM が定めるリフレッシュ周期 規格を満足しなくなる。

## 表示域と映像メモリーの水平方向の大きさを独立に定義

CPUがGDCに送出する映像メモリー・アドレスは絶対番地で与える。X、Yの座標による方が、より直接的であるように

図 6 グラフィック・モード時のドット修正法。描画時,GDC に読み込まれた 16 ビットの映像メモリー内容に対して修正を加える。修 正用ゲート群は各ビットに 1 個割り当てているので dAD をすべて"1"とすると全 16 ビットに対して同時に修正を加え得る

見えるが、汎用性や拡張性を損なってしまう。座標原点位置の 定義や、X、Y座標の変化域など応用装置にとっては予期し得 ない不確定要素が数多くあり、ハードウェアとの一体性が欠如 するためである。アドレスを絶対番地で与えると映像メモリー 構成を自由に選択でき、表示とは無関係な分野での大容量メモ リー制御用としての応用も開ける。

水平方向の表示域と映像メモリーの大きさとを、独立に最大 255 アドレスまでコマンドによって定義できる。このため、表示 域やメモリーの大きさを、512×512 や 1024×1024 のように 256 または 512 ドット単位で定義する必要はない。 水平方向に対し ては 2 アドレス 32 ドット単位で 255 アドレス 4064 ドットまで

図7 4種類のドット修正モード。プログラムで任意に設定できる描画バターンに従って、4種のドット修正モードを選択できる。 EXOR、NAND、ORによるドット単位論理演算としてとらえ得る

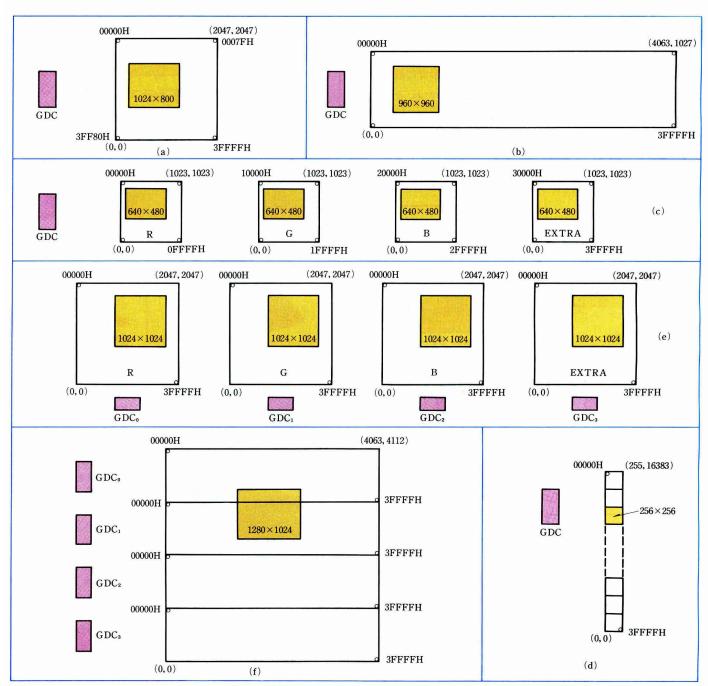

設定でき、垂直方向のドット数は映像メモリーの記憶容量によって決定される。図8に示すような種々のメモリー構成、表示域定義ができる。例えば、図8(b)のように、水平方向に4064ド

ットを定義した時, 垂直方向には最大 1028 ドットを定義できる。一般に使用される CRT の縦横比 (アスペクト・レシオ) は約3:4 である。この CRT に 512×512 の表示を行うと 1 ドット

図8 映像メモリー構成と表示域の設定例。映像メモリー領域と表示領域を独立にコマンドで設定できるので装置設計上,融通性がある。GDC の並列動作によって,更に拡張性が増す

が正方形とならず、円が楕円として表示される。この時、表示域定義を縦横比に合わせて、例えば 480×640 ドットとすれば、円は円として表示できる。表示開始アドレスを変更するコマンドにより、表示域を全方向にドット単位でパニングし、図における非表示域を表示することもできる。X、Y 座標値と絶対番地との変換は映像メモリー構成に従って CPU でのソフトウェアによって次のように簡単な操作で行える。

図 8(a) のように、座標原点 (0,0) をメモリー・マップ左下に取り、X、Y 座標最大値を  $X_{MAX}$ 、 $Y_{MAX}$  とする。マップ左上を0 番地とし左から右へ走査され、アドレスが"1"ずつ増加する。

水平方向アドレス総数 Pは

$P = INT \{(X_{MAX} + 1)/16\}$

ある点 (X, Y) のワード・アドレス (EAD) およびドット・アドレス (dAD) は

$EAD = P * (Y_{MAX} - Y) + INT(X/16)$

dAD = REM(X/16)

ここで、INT は整数部、REM は剰余部を示す。アドレスは加減算およびシフト操作により容易に導出できる。INT(X/16) は X の 4 ビット右シフトにより、REM(X/16) は X の下位 4 ビットを残し、上位ビットを"0"にすれば求められる。更に、P の値が"2 のべき乗"であれば  $P*(Y_{MAX}-Y)$  は  $(Y_{MAX}-Y)$  の左シフト操作によって得られる。

#### 21 種類のコマンドを解釈する

GDC は、表 1 に示す 21 種のコマンドを解釈する。各コマンドは8 ビットで構成され、必要に応じてパラメータを付随させて使用する。標準的な 8 ビットまたは 16 ビットのプロセサで制御できる。CPU が供給するアドレス信号 (図 4 中の  $A_0$ ) は、書き込み信号 ( $\overline{WR}$ )、読み出し信号 ( $\overline{RD}$ ) との組み合わせによって、データ・バス信号 (DB $_{0-7}$ ) の種別を表 2 のように定義する。コマンド/パラメータ転送時および FIFO 内容読み出し時には、CPU は前もって  $A_0=0$ 、 $\overline{RD}=0$ 、 $\overline{WR}=1$  によってデータ・バス上に出てくるステータス・フラグを検出し、FIFO の状態を把握している必要がある。8 種のステータス・フラグが用意されている (表 2)。コマンド/パラメータ転送には次の方法があり、用途に応じて選択する。

- ① FIFO FULLが"0"であることを確認して転送する。

- ② FIFO EMPTY が "1" であることを確認して、最大 16 バ

イトを連続転送する。この時、主記憶-GDC 間 DMA 転送によって高速転送してもよい。

FIFO 内容読み出し時には、次のようにして行う。

- ① DATA READY が"1"であることを確認して読み出す。

- ② FIFO FULL が"1"であることを確認して、16 バイトを連続的に読み出す。この時、GDC-主記憶間 DMA 転送によって高速読み出ししてもよい。

FIFO は CPU から見て、読み出し/書き込み兼用として動作する。初期化動作以後、書き込み専用として動作し、描画アドレス制御部や制御 ROM が個々の処理を実行中である時にはコマンド/パラメータを一時的に蓄積する。上記処理が終了すると即座に FIFO 内容は取り出され、制御 ROM はその解釈処理を開始する。READ などの読み出しコマンドが FIFO から取り出され、解読されると、CPU からなんらかのコマンドが発行され

表 1 コマンド・リストと動作の内容。21種のコマンドを持ち、可 変パイト数のパラメータを付加して使用する。いったん FIFO に蓄 積された後、制御 ROM を駆動して諸制御機能を達成する

| コマンド         | 動作内容                  |

|--------------|-----------------------|

| 動作制御         |                       |

| RESET        | 初期化動作                 |

| SYNC         | 動作モード、同期信号波形の定義       |

| MASTER/SLAVE | マスタ動作, スレーブ動作の選択      |

| 表示制御         |                       |

| START        | 表示の開始の指示              |

| STOP         | 表示の停止の指示              |

| ZOOM         | 拡大表示係数, 拡大描画係数の設定     |

| SCROLL       | 表示開始アドレス、表示領域の設定      |

| CSRFORM      | 文字表示時のカーソル形状などの設定     |

| PITCH        | 映像メモリー水平方向ワード数の設定     |

| LPEN         | ライトペン・アドレスの読み出しの指示    |

| 描画制御         |                       |

| VECTW        | 描画に必要な各種パラメータの設定      |

| VECTE        | 直線、四辺形、円弧描画の実行の指示     |

| TEXTW        | グラフィックス・テキスト・コード設定    |

| TEXTE        | グラフィックス・テキスト描画実行指示    |

| CSRW         | 描画アドレスの設定             |

| CSRR         | 描画アドレスの読み出しの指示        |

| MASK         | マスク・レジスタ値の設定          |

| 映像メモリー制御     |                       |

| WRITE        | パラメータの映像メモリーへの書き込み準備  |

| READ         | 映像メモリー・データの読み出しの指示    |

| DMAW         | 映像メモリーへの DMA 転送開始の指示  |

| DMAR         | 映像メモリーからの DMA 転送開始の指示 |

るまで、FIFO は CPU 側から見て読み出し専用として動作する。つまり、映像メモリー内容や内蔵レジスタの内容を連続的に蓄積する。同時に、最初に蓄積されたデータは FIFO から取り出され、GDC 上のレジスタ(図 2 には示していない)にセットされる。それによって、ステータス・フラグ(DATA READY)が "1" になる。前述のように、ステータス・フラグ読み出し条件を満足する信号、すなわち、 $A_0=0$ 、 $\overline{RD}=0$ 、 $\overline{WR}=1$  を (GDC が非選択時に)外付け回路によって与えると、ステータス・フラグは  $DB_{0\sim7}$  端子から静的な出力信号として取り出せる。タイマ割り込み (VSYNC)、ライトペン検出割り込み (LPEN)、FIFO BUSY (FIFO FULL) などのハードウェア・ハンドシェーク用信号として使用できる。

#### SYNC コマンドによって動作モードを選ぶ

SYNC コマンドの構成を図9に示す。このSYNC コマンドの第1パラメータ中のCHR およびGのビット操作によって、次の3種の動作モードのうちの任意の1種を選択する。

- (1) グラフィック・モード

- (2) 文字/グラフィック混在モード

- (3) 文字モード

動作モードの選択によって、描画時の描画アドレス計算およ

表2 データ・バス信号内容とステータス・フラグ。4種の8ビット構成のデータ・バス信号を読み出し/書き込みする。下位3ビットのステータス・フラグをコマンド・レベルでのCPU-GDC間データ転送時に使用する

| データ・ハ     | データ・バス信号内容          |                     |  |  |  |  |  |  |  |

|-----------|---------------------|---------------------|--|--|--|--|--|--|--|

|           | $\overline{RD} = 0$ | $\overline{WR} = 0$ |  |  |  |  |  |  |  |

| $A_0 = 0$ | ステータス・フラグ読み出し       | パラメータ書き込み           |  |  |  |  |  |  |  |

| $A_0 = 1$ | FIFO データ読み出し        | コマンド書き込み            |  |  |  |  |  |  |  |

| ステータ | ス・フラグ            |               |

|------|------------------|---------------|

| DB   | 名称               | 状態            |

| 0    | DATA READY       | 読み出しデータのセット終了 |

| 1    | FIFO FULL        | FIFO内容満杯      |

| 2    | FIFO EMPTY       | FIFO内容空白      |

| 3    | DRAWING          | 描画実行中         |

| 4    | DMA EXECUTE      | DMA 転送中       |

| 5    | VERTICAL SYNC    | 垂直同期信号期間      |

| 6    | HORIZONTAL BLANK | 水平消去期間        |

| 7    | LIGHT PEN DETECT | ライトペン光検出終了    |

図9 SYNC コマンド。コマンド/パラメータは8ビット構成であり、コマンドは処理の実行や方向付けを行う。パラメータはレジスタ値の設定などに使われる

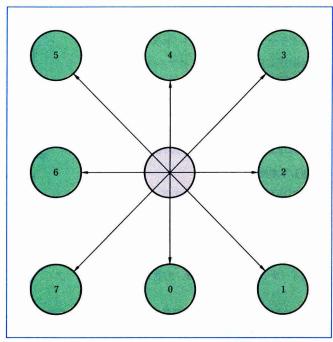

図10 描画方向の定義。45 度単位で8通りの描画開始時基線方向を 定義する。GDC内での描画アドレス演算時, 描画方向変化が検出さ れると一時的に方向値を変化させて, アドレス算出する

び表示データの修正法や AD<sub>0~15</sub>, A<sub>16</sub>, A<sub>17</sub> の端子機能に変化を与える。表示アドレス制御部や同期信号発生部の動作は不変である。グラフィック・モードではドット単位描画制御を行うため、描画ワード・アドレス EAD だけでなくドット・アドレス dAD をも算出する必要がある。GDC のように 16 ビットすべての映像メモリー内容をチップ内に読み込み、修正を加える形を採ると、ドット・アドレスは外部に出力されないので、装置設計者はドット・アドレスの役割について、意識しなくてもよい。描画アドレス演算は図 10 の描画方向指示に従って、表 3 のようにして行われる。方向 (DIR) が "3"、すなわち、左下から右上 45 度方向に描画方向が設定されている時、ワード・アドレスを水平方向総アドレス数だけ減算し、ドット・アドレス・レジ

スタの内容を左方向(上位方向)に1ビット回転する。これは,

表示時、1本上の走査線でドット位置が右に1ドット移動した

表3 描画方向に基づく描画アドレス演算。グラフィック描画時にのみ行うドット・アドレス(dAD)演算は左右方向への回転動作によって達成する。MSBまたはLSBが"1"の時、描画ワード・アドレスEAD演算が追加される

|     | ノーレス EAD 似弁の 追加される                                                                                                                |             |

|-----|-----------------------------------------------------------------------------------------------------------------------------------|-------------|

| DIR | グラフィック描画時                                                                                                                         | 文字描画時       |

| 0   | EAD+P→EAD                                                                                                                         | EAD+P→EAD   |

| 1   | $\begin{array}{l} EAD+P \longrightarrow EAD \\ dAD(MSB)=1 \colon EAD+1 \longrightarrow EAD \\ dAD \longrightarrow LR \end{array}$ | EAD+P+1→EAD |

| 2   | $dAD(MSB)=1: EAD+1 \longrightarrow EAD$<br>$dAD \longrightarrow LR$                                                               | EAD+1→EAD   |

| 3   | $\begin{array}{l} EAD-P \longrightarrow EAD \\ dAD(MSB)=1 \colon EAD+1 \longrightarrow EAD \\ dAD \longrightarrow LR \end{array}$ | EAD−P+1EAD  |

| 4   | EAD-P→EAD                                                                                                                         | EAD−P→EAD   |

| 5   | $\begin{array}{c} EAD-P\longrightarrow EAD \\ dAD(LSB)=1\colon EAD-1\longrightarrow EAD \\ dAD\longrightarrow RR \end{array}$     | EAD−P−1→EAD |

| 6   | $dAD(LSB)=1: EAD-1 \longrightarrow EAD$<br>$dAD \longrightarrow RR$                                                               | EAD−1—EAD   |

| 7   | $\begin{array}{c} EAD+P\longrightarrow EAD \\ dAD(LSB)=1\colon EAD-1\longrightarrow EAD \\ dAD\longrightarrow RR \end{array}$     | EAD+P-1→EAD |

注) EAD: ワード・アドレス dAD: ドット・アドレス LR:左方向回転 RR:右方向回転

P: 水平方向総アドレス数

点のアドレスを意味する。CPU が描画開始時の方向を設定した後、描画中には GDC が描画アルゴリズムに従ってドットごと

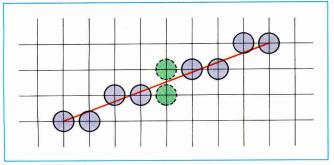

図11 直線描画の例。X 方向に座標をドット単位で移動する。Y 座標小数部が四捨五入条件を満足すると、Y 座標を増加する。 描画方向を 180 度変更すると、境界点(●のドット)で Y 座標位置の再現性がないが、ソフトウェアによって回避できる

に描画方向を算出する。図 11 の直線描画例では、CPU は方向 "2"を与える。第 3 点に対するアドレス演算時、一時的に "3" に変更され 45 度右上の点をアドレスする。

文字モード時あるいは文字/グラフィック混在モード時でグラフィックス描画を行わない時、ドット・アドレス(dAD)はビット・マスク用として動作し、ポインタ(PS)の機能は無視される。ドット単位のアドレス演算は不要であり、パターン・レジスタ(PTN)に格納する文字コードをそのまま映像メモリーに送出すればよいからである。ただし、REPLACE など 4種のドット修正機能は生かされている。文字描画時には、図 12 に示すように、dADが"1"のビットに対応する修正前データ(映像メモリー内容)と PTN データに対して各修正を実行する。dAD 内容は MASK コマンドによって、図 12 のように任意値

図 12 文字モード時のドット修正法。ドット・アドレス・レジスタ dAD が"1"のビットに対応するデータにのみ修正を加える。ポインタの機能は無視される

に設定できる。特に、文字モードでは文字属性設定ビットに対するビット・マスク操作や上位/下位バイトの判別などに、また、グラフィック・モード時には、全ビットを"1"とし16ドット同時描画を行う映像メモリーの高速クリアなどに有効である。グラフィック・モード時であっても、dADの MSB(most significant bit)と LSB(least significant bit)が常に"1"であるため、ワード単位で描画アドレス計算が行われる(表3参照)。SYNCコマンドの第1パラメータでは動作モード設定のほかに、Dはリフレッシュ有無指定、Iはインタレース走査指定、Fは描画タイミングの選択を行う。Fを"1"に設定すると、水平および垂直の表示消去期間にのみ描画動作を起こすので、表示にフラッシュを生じない。ただし、表示期間にも描画を行う"F=0"の場合に比べて、平均化した描画速度は約1/5程度となる。第2パラメータ以降の設定でフロントポーチ、バックポーチ

# 描画アルゴリズムの改善

ラスタ走査型 CRT を用いたグラフィック装置で直線や円弧などを描画することは、1画面分以上の容量を持つ映像メモリーに対して、ビット単位でデータ修正を加えることを意味する。水平方向に対してはビット単位、垂直方向に対しては走査線単位で区切られた格子の交点上に、ドットを描画し、表示の場合は、その映像メモリーを読み出して表示する。元来、直線や円弧などは連続的に値が変化するアナログ量なので、それを格子の交点上のドットとして近似し量子化するために、描画装置はなんらかの処置をする必要がある(本文中の図11参照)。これを達成する一番簡単な方法は、あらかじめ座標変位テーブルを多数用意しておき、描画の種類に従ってテーブル参照の方法を変更しながら描画する近似的な手法である。しかし、描画結果に部分的な歪が生ずる場合が多く、好ましくない。

描画精度を向上させるには、方程式の解を求める方法が一番確実である。通常、水平または垂直方向について最小ドット単位刻みで座標を移動しながら、もう一方の座標値を導出する。図 11 の例では、X 軸方向に座標を"1"ずつ移動しながら Y 座標を算出する。式を解いた結果得られた座標値は実数なので、小数部を四捨五入することにより整数座標位置に近似する。誤差は ±0.5 座標以内に収まる。したがって、整数座標格子に対す

を持つ水平/垂直同期信号幅および表示期間を定義する。これらの値は水平関係を2クロック、垂直関係を1走査線単位で定義できるので、NTSC (National Television System Committee)のテレビジョン放送基準に合致した同期信号を生成できる。MASTER/SLAVE コマンドによってGDC をスレーブ動作設定した場合、外部同期信号を受け付け、その降下時に同期信号発生部を初期化する機能を持つ。このため、多数個のGDC を同一システム内で互いに同期が取れた状態で並列動作することや、テレビ・カメラなどの映像機器から出力される映像信号にGDC が制御する映像信号を重畳することなどが可能である。

#### 描画の実際

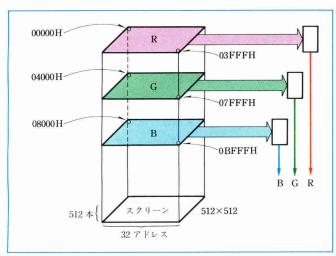

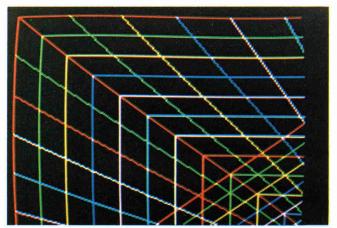

図13は、512×512ドットの解像度で直線および四辺形を、白を含む7色表示した例である。この描画装置の映像メモリー構成は図14のようになっている。四辺形部は、対角線上の点(0、

る近似としては誤差がない。図 11 の例では,Y 座標の変位は "0" または " $\pm 1$ " なので,描画開始時の座標が既知であり,そ の値が記憶されているならば,算出される整数部データは使用 する必要性がない。

座標変化が生じる状態の検出だけが行えれば、あらかじめ記憶しておく描画開始時の座標値を ±1 することにより描画点の座標を算出できる。換言すれば、小数部演算の結果のみに注目し、その結果と "1/2" との大小比較を行えば、整数部は容易に導出できる。ただし、方程式をそのままの形で演算したのでは、実数乗除算や三角関数演算を実行せねばならない。更に、これらの演算は 1 ドット描画ごとに実行するので、たとえ高速のCPU や演算専用 LSI を用いたとしても、描画速度の飛躍的な向上は期待できない。原点に立ち戻って、描画アルゴリズムを考え直す必要がある。

#### 整数加減算だけで描画点を算出

そこで GDC では、方程式の解のうち小数部の結果のみに注目しつつ描画点を導出する方法を等価的に実行する方式を採っている。座標が変化した時の小数部データの変位がどの程度の大きさになるかを GDC が容易に判別できるように、CPU は後述する描画用パラメータを1回の描画の実行に先立って、1回だけ算出する。パラメータは GDC に送出され、GDC はこのパラメータを用い整数加減算処理だけで連続的に描画点を算出す

0)、(511,511)を結ぶ四辺形から X、Y 座標を"16"ずつ移動した 16個の四辺形と、(255,0)、(255,511)を結ぶ 45 度傾斜四辺形から同様に X、Y 座標を移動した傾斜四辺形で構成されている。順次、色を変化させながら描画した。白の描画時にはR、G、B 各メモリー・プレーンに対して、同一座標異描画アドレスに各々同一の描画を行う。総計 4 万 1280 ドットを描画している。直線部は、(0,0)、(511,511)を結ぶ直線から始め、同様に座標と色を変化させ 32 本の直線描画を行い、総描画ドット数は2 万 6624 ドットである。0.1 秒程度で瞬間的にこれらの描画をすべて終了する。円弧描画においても、この描画速度は変わらない。描画基線の傾きが 45 度単位であれば、四辺形および矩形領域に対してドット単位連続描画を行うグラフィックス文字描画を、一括して高速描画する機能を持つ。45 度以外の場合は直線描画の集合として実現する。文字をドットで表現する方法と

して、直線描画によって文字形成するストローク法がある。こ の方法は描画単位がドットではなく直線であるため細かいアク

図13 白を含む7色で直線,四辺形を描画した例

る。

2点間の直線補間を行う直線描画の場合には、次のようなアルゴリズムに従って描画用パラメータを決定している。2点間のXおよびY座標の変位を、それぞれ、 $\Delta X$ 、 $\Delta Y$ とすると、直線の方程式は次式で表せる。

$$(\Delta Y/\Delta X) * N = I + F \tag{1}$$

N: X 座標値。"1" から始まり"1" ずつ変化する。

I:Y座標の整数部。描画開始点からの変位を示し、開始点では"0"。

F: Y座標の小数部。

小数部のみに注目して式(1)を変形し,四捨五入の条件を加味すると式(2)が得られる。

$$F = (\Delta Y / \Delta X) * N - I \ge 1/2 \tag{1}$$

$$2 * N * \Delta Y - (2 * I + 1) * \Delta X \ge 0 \tag{2}$$

N を "1" ずつ変化させながら式(2)の正負判定を行えば、Y 座標の変化点が得られる。式(2)は実数を含まず整数 ( $\Delta X$ ,  $\Delta Y$  も整数) だけで表現されるので、このままの形で直接演算しても構わないが、X 座標変化時の式(2)の差分、つまり、N=n の時と、N=n+1 の時の式(2)の値の差が既知ならば、整数加減算のみによって式(2)の結果が算出できる。すなわち、ある点の式(2)の値と、その差分が与えられれば、次の描画点における式

(2)の値が得られる。したがって、CPU は次の(a)~(d)で示す 4 種の描画用パラメータを演算生成し、GDC に送出する。

- (a) 第1回目の描画アドレス計算に必要な式(2)の初期値データ。

- (b) 式(2)が正の時,次の描画点における式(2)を導出するための差分データ

- (c) 式(2)が負の時, 次の描画点における式(2)を導出するための差分データ

- (d) 最大描画ドット数

ここで、(d)は描画終了点の検出のために使用する。(a)は、式 (2)において、N=1、I=0 の場合に相当する。したがって、

$$2*\Delta Y - \Delta X$$

(a

式 (2) が正の時,次回の描画点における式 (2) は N および I を ともに "1" だけ加算したものとなる(直線描画の場合は,傾き が  $0\sim45$  度の範囲内に入るように取り扱うため)。したがって,その差分は

$$2*(\Delta Y - \Delta X) \tag{b}$$

負の場合, N のみを"1"だけ加算したものとなる。したがって,

最大描画ドット数は,

$$\Delta X$$

(d)

で求められる。

図 14 512×512 ドットの 7 色グラフィック表示時の映像メモリー・プレーン構成例。表示時には 0H から 3FFFH のアドレスを与え、R, G, B の 3 枚のプレーンから同時に映像出力を得る

図11において、左下から右上の点へ描画する場合と、逆方向への描画の場合とが考えられる。四捨五入法に基づく描画を行うので、小数部演算結果が境界値の"1/2"とならなければ、描画開始点がどちらにあろうとドット描画位置には再現性がある。しかし、描画進行方向に依存した描画座標の移動を行うので、境界値を持つドットがあると図の破線で示したドットのように位置ずれを生じる。同一図形のドット反転修正モードでの再描画による図形の選択的消去が不完全となる。しかし、描画方向の選択に制限を加え、描画開始点を一定とする単純なソフトウェア処理を施せば、この欠陥は除去できる。

円弧描画は、1/8 弧を基本描画単位にしている。全円を描画するには、1/8 弧を 8 回描く。直線描画の場合と同様、小数部の四捨五入法を採用している。詳細は述べないが、半径を r とした時、措画ドット総数、描画開始点からのマスキング・ドット数および (r-1)、2(r-1)、-1の5種のパラメータを作成し、GDCに設定する。そうすると、直線描画の時と同様、GDCは加減算操作だけで1/8 弧を描くためのアドレスを計算できる。CPUでのパラメータ算出の際に、1~2回乗除算が必要になるが、1回の円弧描画について一度だけでよい。GDC内での描画アドレス計算は直線描画の場合と同一なので、描画速度は桁違いに速くなる。なお、CPUから GDC へ渡す描画パラメータは、本文中の表 4 にまとめてある。

セントをつけにくく、描画品質が良くない。GDC を使用して文 字表現する時, ストローク方式を併用し文字を回転させてもよ い。直線や円弧は、どのような方向に対しても描画できる(図 15)。描画速度は描画方向に全く依存しない。

GDC に描画実行させるには、CPU のソフトウェアやディジ タイザなどで座標を発生させ、この値を基にして CPU は、GDC が解釈できるレベルの、よりマイクロなコマンド/パラメータを 作成する(これを描画前処理と呼ぶ)必要がある。次のような 段階を経る。① 実線, 破線などの線種を選択する。② REPLACE などのドット修正モードを選択する。③座標-絶対アドレス変 換を行い, 描画開始アドレスを算出する。④ 直線, 円弧などの 描画種類や描画方向を図15,表4に従って決定し、描画パラメ ータを算出する。⑤ 描画実行の指示をする。VECTE, TEXTE,

WRITE コマンドに続くパラメータ入力,の3種の描画実行コ マンドを持つ。

図13の描画実行時,表5のコマンド/パラメータをCPUは GDC に送出している。まず、TEXTW で実線(FFFF)、WRITE で COMPLEMENT 修正を指定している。これらの指定は変更 がある時のみ行えばよい。2回目の描画では特に設定していな い。R(レッド)のメモリー・プレーン上の表示画面左下隅に定 義した座標(0,0)に相当する描画開始絶対ワード・アドレス "3 FE0"とドット·アドレス"0"を CSRW で設定した後、図 10、 図 15, 表 4 に従って、VECTW により描画方向と描画パラメー タを設定する。1回目の描画時の方向は"3"であるが、2回目 は "2" となる。描画パラメータの負数は "2 の補数" 表現する。 描画実行コマンド実行前に送出するコマンドの送出順には制限

グラフィックス 傾斜グラフィッ DIR 直線 円弧 四辺形 DMA 文字 クス文字 0 1 2 4 5 6 •:描画始点 → : 描画方向 :描画域

図 15 描画開始時の描画方向選択。直線描画では 1/8 領域内に含まれる直線を 1 個の描画方向で表現する。 全円描画の場合には描画始点と描画方向を変化させ、1/8弧を8回描画して形成する

: 定義域

はない。描画実行時に所期の値 が設定されていればよい。表5 に示すように1回の描画に要す るコマンド/パラメータ総数は, 直線描画時 15, 四辺形描画時に は 17 で済む。内蔵 FIFO の容量 は16バイトであるので,描画実 行中に次の描画用として送出さ れるコマンド/パラメータをほ とんどすべて蓄積できる。した がって, 描画を間断なく実行す

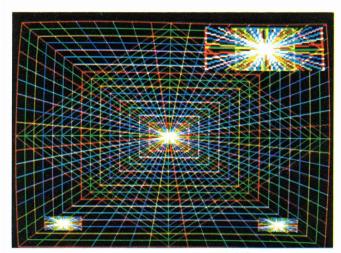

図16は、メモリー-メモリー 間 DMA 転送およびグラフィッ クス文字拡大描画の例である。 中央部の64×32ドット矩形領 域を選択的に映像メモリーから 主記憶へ、各メモリー・プレーン ごとに1回、計3回のDMAR コマンド発行によって DMA 転送し、そのパターンを左右下 隅の2カ所に計6回の DMAW コマンドによって, 主記憶から DMA 転送した。4 クロック/バ イトの速度で、バイト/ワード変換を実時間で行いつつ、連続的なメモリー-メモリー間バースト DMA 転送を実現する。バスの分離がなされていない場合のメモリー間 DMA 転送の場合

と比較して、2倍以上高速である。同一図形の描画が多い時には、異なる映像メモリーに図形セルを描画し、任意個所への DMA 転送を繰り返してもよい。前記パターンを3倍に拡大し

表 4 描画パラメータ設定値。描画アルゴリズムに従って必要とされる描画パラメータを設定する。最大 5 種 10 バイトのパラメータを作成し GDC に送出するだけで,GDC は描画を実行する

|                                  | DC                     | D                          | $D_2$                     | $\mathbf{D_i}$ | DM  |                                                                      |

|----------------------------------|------------------------|----------------------------|---------------------------|----------------|-----|----------------------------------------------------------------------|

| 初期値                              | 0.                     | 8                          | 8                         | -1             | -1  |                                                                      |

| 直線                               | ΔX                     | $2 \Delta Y  -  \Delta X $ | $2 \Delta Y -2 \Delta X $ | 2 4Y           |     | 注)                                                                   |

| <b>д</b> . 1 - 1 - 1 - 1         | $(r/\sqrt{2})\uparrow$ | r-1                        | 2(r-1)                    | -1             | 0   | ΔX: X 座標変位<br>ΔY: Y 座標変位                                             |

| <u> </u>                         | N                      | r-1                        | 2(r-1)                    | -1             | М   | r: 半径                                                                |

| 四辺形                              | 3                      | A*1                        | B*1                       | -1             | A*1 | N: 描画総ドット数<br>M: マスキング・ドット数                                          |

| 8×8ドット<br>グラフィックス文字              | 7                      |                            |                           |                | 位一直 | A*1, A*2: 第1描画方向ドット数<br>B*1, B*2: 第2描画方向ドット数                         |

| 8×8ドット以外の<br>グラフィックス文字,<br>塗りつぶし | B*2                    | A*2                        |                           |                |     | A*3: 第1 DMA 方向バイト数<br>B*3: 第2 DMA 方向バイト数<br>D*1: R/W バイト数<br>↑: 切り上げ |

| DMA                              | B*3                    | A*3                        | $(A^{*3}/2)$              | M - M          |     |                                                                      |

| READ/WRITE                       | D*1                    |                            |                           |                |     |                                                                      |

| 1文字<br>1ドット                      |                        |                            | <u>-</u>                  |                |     |                                                                      |

表 5 図 13 の描画実行時, CPU が GDC に送出するコマンド/パラメータの実例。直線部, 四辺形部共に描画開始時と 2 回目の描画時の場合について示した

| ●直線描画  |                             | コマンド名                        | С                          | Pı             | $P_2$          | Ps       | P4 | $P_{5}$        | $P_6$          | P <sub>7</sub> | P <sub>8</sub> | P <sub>9</sub> | P <sub>10</sub> | Pii |

|--------|-----------------------------|------------------------------|----------------------------|----------------|----------------|----------|----|----------------|----------------|----------------|----------------|----------------|-----------------|-----|

|        | (0,0)<br>↓<br>(511,511)     | TEXTW WRITE CSRW VECTW VECTE | 78<br>21<br>49<br>4C<br>6C | FF<br>E0<br>0B | FF<br>3F<br>FF | 00<br>01 | FF | 01             | 00             | 00             | FE             | 03             |                 |     |

|        | (0,16)<br>↓<br>(511,495)    | CSRW<br>VECTW<br>VECTE       | 49<br>4C<br>6C             | E0<br>0A       | 7B<br>FF       | 00<br>01 | 7F | 01             | 80             | FF             | 7E             | 03             |                 |     |

| ●四辺形描画 |                             | コマンド名                        | С                          | Pi             | P <sub>2</sub> | Ps       | P. | P <sub>5</sub> | P <sub>6</sub> | P7             | P <sub>8</sub> | P <sub>9</sub> | P10             | Pn  |

|        | (0,0)                       | TEXTW WRITE CSRW VECTW VECTE | 78<br>21<br>49<br>4C<br>6C | FF<br>E0<br>42 | FF<br>3F<br>03 | 00 00    | FF | 01             | FF             | 01             | FF             | FF             | FF              | 01  |

|        | (16, 16)<br>,<br>(495, 495) | CSRW<br>VECTW<br>VECTE       | 49<br>4C<br>6C             | E1<br>42       | 7 D<br>03      | 00       | DF | 01             | DF             | 01             | FF             | FF             | DF              | 01  |

図 16 図 13 の一部をメモリー-メモリー間 DMA 転送し, 拡大描画した例

図17 図13の一部の3倍拡大表示例

図18 パニングにより図13の中央部を表示した例

て図 16 の右上に描画した。グラフィックス文字描画は、ドット 単位連続描画による任意のドット構成、文字外形、文字幅を持 つ文字描画や矩形領域塗りつぶし描画だけにとどまらず、この ような画像データの拡大描画にも応用できる。

描画時以外に表示時にも拡大制御機能を持つ。各々、拡大係数として1~16の整数を ZOOM コマンドで設定できる。図 17では、表示開始アドレスを変更せずに図 13の左上部を 3 倍に拡大して表示した。拡大描画とは異なり、映像メモリー内容には変更がない。表示のタイミング制御のみを行うだけなので、瞬時に拡大できる。表示をこのように拡大すると不可視領域が生ずる。この不可視領域を表示するため表示領域を上下左右にドット単位で移動するパニングを SCROLL コマンドによって実現できる。図 18 は、パニングの結果、中央部を表示した例である。拡大表示時のほかに、表示領域より映像メモリー領域を大きく定義した場合にもパニングが応用できる。

描画実行に先立ち、CPUが算出しVECTWコマンドによってGDCに与える、描画パラメータの各種描画における値を表4に示す。直線、円などのグラフィックス描画だけでなく、DMA転送数や映像メモリー内容の読み出し/書き込み転送数制御にも使用する。このように描画パラメータ算出は簡略化されており、短時間で求められる。演算結果はGDCが描画処理実行中であってもFIFOに転送し蓄積できる。したがって、CPUによる描画前処理とGDCによる描画アドレス演算および映像メモリーに対する実質的な描画の、従来3段階に分けて実行していた処理を分散同時処理でき、高速で高性能な描画機能を持つ。高速のCPUや演算専用LSIを用いると、描画前処理はより高速化でき、高性能なグラフィック装置を構成できる。現用装置と比較する時、描画機能のみを取り上げても飛躍的な改善がなされており、直線描画で10倍、円描画で1000倍以上の描画速度を実現した。

#### グラフィック表示以外への応用範囲も広い

同期信号や表示アドレスの発生のみを行う従来型 CRTC とは異なり、高速グラフィックス描画、多数個の並列動作、大容量メモリー制御、ダイナミック RAM に対するリフレッシュ、DMA 転送などの諸機能を持っているため、表示とは無関係な分野への応用もあり、応用範囲は極めて広い。

カナや英数字だけでなく, 漢字表示機能を持つ表示装置が普

及してきた。英数字などと同様に、漢字の情報処理コードが日 本工業標準規格 (JIS) によって決められている3 7ビット・コ ード2バイトで構成される14ビットであり、3000字以上を指 定している。カラー表示など種々の文字属性を1字ごとに付加 した漢字表示を行うには,文字属性制御ビットを含めると16ビ ットを超える情報が必要で、制御が複雑となる。従来の DMA 転送型 CRTC では、内蔵行バッファの記憶容量および構成から 文字コードとして使用できるビット数は最大8に固定されてお り、漢字表示制御用としては使用できなかった。GDC が制御す る映像メモリーの1アドレスには最大16ビットの情報を格納 するので、漢字表示時には少なくとも2個のアドレスにまたが って文字属性を含む漢字1字分の情報を設定し、表示サイクル においてはその情報を同時にアクセスせねばならない。GDC は 表示サイクル時の表示アドレス進行を通常の"1"ではなく、"2" によるインクリメント形態を採る機能を持つ。したがって、1表 示サイクルに連続した2個のアドレスの表示データを同時に取 り出すことが容易である。各々のアドレスに文字コードと文字 属性コードを分割して設定してもよい。この機能は、漢字表示 への応用のほかに、GDC のクロック周波数を規格以上に高くせ ずに、1行中の表示文字数を100字以上必要とする高解像度文 字表示や 1024×1024 ドット以上のノーインタレース高解像度 グラフィック表示への応用を可能にする。

このほか、GDCは、表示結果をハードコピーする際の、グラフィック装置とプリンタとのインタフェース設計を容易にし、また、図表の作成を含むワード・プロセサへの応用に対しても大きな威力を発揮するだろう。また、フロッピー・ディスク用バッファ・メモリー制御用など、多分野への応用が考えられている。

#### 参考文献

- Johnson, S., "Fast Raster-Scan System Displays Graphics and Images," Electronic Design, vol. 28, no. 10, pp. 205-208, May 10, 1980.

- Oguchi, T., Higuchi, M., Kamaya, M., Uno, T. and Suzuki, M., "A Single-Chip Display Controller," Digest of Technical Papers, 1981 IEEE International Solid-State Circuits Conference, pp. 170-171, Feb. 1981.

- 3)日本規格協会「JIS C 6226」, 『JIS ハンドブック 情報処理 1981』, pp. 126-185, 1981 年 4 月.

- 4) 小口, 樋口, 鎌谷, 鵜野「グラフィック制御用 LSI」, 『NEC 技報』, pp. 58-63, 1981 年 6 月.